MAIN PAGE

> Back to contents

Cybernetics and programming

Reference:

Myasnikov V.I.

Generation algorithm for high-precision PWM signal

// Cybernetics and programming.

2018. № 5.

P. 24-31.

DOI: 10.25136/2644-5522.2018.5.18991 URL: https://en.nbpublish.com/library_read_article.php?id=18991

Generation algorithm for high-precision PWM signal

Myasnikov Vladimir Ivanovich

PhD in Technical Science

Associate Professor, Department of Information and Computing Systems, Volga State University of Technology

424000, Russia, respublika Marii El, g. Ioshkar-Ola, ul. Pl. Lenina, 3

|

MyasnikovVI@volgatech.net

|

|

|

|

DOI: 10.25136/2644-5522.2018.5.18991

Received:

28-04-2016

Published:

25-11-2018

Abstract:

The object of the study are regulators, built on the basis of pulse-width modulation (PWM). The popularity of regulation using PWM is explained by the simplicity of its implementation, the absence of hysteresis in the executive electromagnetic device. The bit width and frequency of the PWM signal affect the quality of regulation. Modern microcontrollers have an integrated PWM module, so the implementation of the control device on them is simple and inexpensive. Given the parameters of the PWM signal - frequency and bit depth, the developer often faces difficulty in implementing the controller due to the limited resources of the microcontroller, in particular, the clock frequency. The paper analyzes the specified N-bit PWM by splitting it into two components, one of which is determined by the frequency and width of the PWM processor. The dependence of the required memory size is investigated depending on the algorithm of splitting into components, as well as on the bit depth of the microcontroller used. As a result of the research, the memory costs for a tabular method for generating a PWM signal depending on the width of the microcontroller used are determined. The main result of the work is the possibility of increasing the resolution of the controller with limited microcontroller resources. Recommendations on the implementation of the algorithm depending on the selected microcontroller are given, the required memory resources are given.

Keywords:

microcontroller, PWM, algorithm, spectrum, filtering, resolution, memory size, rate, accuracy, frequency

This article written in Russian. You can find original text of the article here

.

В качестве исполнительного механизма регуляторов расхода газов в хроматографических комплексах используется электромагнитный клапан. Степень поддержания и шаг изменения задания расхода газа определяется точностью формирования управляющего воздействия (напряжения), подаваемого на клапан.

В высокоточных регуляторах используются управляющие сигналы с разрешением до 20 бит. Формирование управляющего сигнала обычно обеспечивается двумя способами: с помощью цифро-аналогового преобразователя (ЦАП) или широтно-импульсного (ШИМ) сигнала [1, 2].

Регулятор на базе ЦАП имеет два недостатка

- ЦАП с высоким разрешением имеет высокую стоимость;

- регулирование электромагнитным клапаном при помощи ЦАП имеет некоторый гистерезис, что приводит к ухудшению точностных характеристик.

Регулятор на базе ШИМ свободен от такого недостатка как гистерезис, кроме того, любой современный микроконтроллер имеет в своем составе модуль ШИМ, что позволяет построить недорогой регулятор. При реализации ШИМ сигнала на микроконтроллере сложность возникает с обеспечением необходимой его частоты. Рассмотрим особенности ШИМ сигналов.

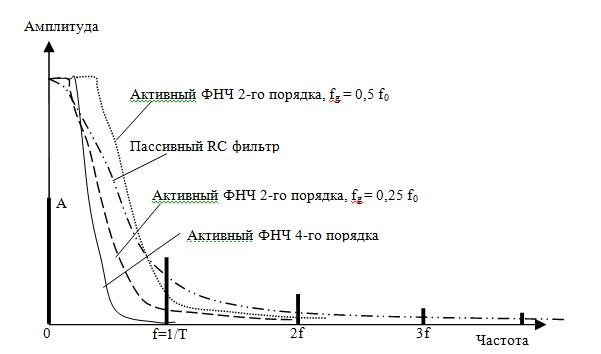

ШИМ сигнал представляет собой импульсную последовательность с постоянным периодом повторения и изменяемой длительностью импульса. Отношение длительности импульса к периоду называется коэффициентом заполнения, который может изменяться в пределах от 0 до 1 или от 0% до 100% [3, 4]. Частотный спектр однополярного ШИМ сигнала с периодом повторения равным Т является дискретным (так как сигнал периодический) и содержит постоянную составляющую – А, первую гармонику (основная частота) f = 1 / Т, и бесконечное число гармоник, частота которых кратна основной – 2f, 3f, 4f … (рис. 1) [5].

Рис. 1.Спектр ШИМ сигнала

Информационным параметром ШИМ сигнала является постоянная составляющая (А) или среднее значение напряжения за период. Зависимость среднего напряжения от величины коэффициента заполнения (Q = 0 ÷ 1) является линейной:

A = Q × VШИМ,

где VШИМ – амплитуда ШИМ сигнала.

Для выделения постоянной составляющей ШИМ сигнал следует пропускать через низкочастотный фильтр (ФНЧ). На рис. 1 приведены АЧХ ФНЧ: простого пассивного RC-фильтра, активных фильтров Баттерворта 2-го и 4-го порядков с граничной частотой (fg), равной 0,25 от частоты первой гармоники (f0) и активного фильтра Баттерворта 2-го порядка с fg = 0,5 f0. Из рисунка видно, что удовлетворительные результаты дает лишь ФНЧ 4-го порядка. Для него подавление в полосе задержания составляет 80 дБ на декаду. ФНЧ 2-го порядка обеспечивает подавление 40 дБ на декаду, а пассивный RC-фильтр лишь 20 дБ. Таким образом, используя ФНЧ с достаточно крутой АЧХ и/или достаточно низкой граничной частотой можно добиться приемлемого подавления гармоник.

Однако при уменьшении граничной частоты ФНЧ будет увеличиваться время установления выходного напряжения фильтра, следовательно, необходимо выбирать такое значение граничной частоты, чтобы обеспечить приемлемое значение переходной характеристики фильтра.

Другой путь для обеспечения приемлемых остаточных флюктуаций на выходе ФНЧ – повышение частоты ШИМ. В этом случае возможно использование фильтров низкого порядка, вплоть до RC-фильтров. Следует отметить, что исполнительные устройства часто представляют собой индуктивную нагрузку (например, клапаны), которые сами являются фильтрами НЧ. В этом случае можно исключить ступень ФНЧ после ШИМ. Использование ШИМ для управления клапанами без ФНЧ позволяет избежать эффекта гистерезиса, т.е. повысить точность регулирования. С другой стороны следует выбирать частоту ШИМ, лежащую за диапазоном слышимости человека, чтобы не появлялись посторонние шумы в процессе работы. Так коллекторные двигатели могут создавать звуковой шум на частотах от 20Гц до 4 кГц. Для исключения этого нежелательного эффекта нужно выбирать частоту выше 4 кГц. Для некоторых клапанов требуется частота ШИМ выше 16 кГц, чтобы обеспечить высокое подавление спектральных составляющих,

Повышение частоты ШИМ при заданной его разрядности часто ограничивается частотой процессора. Так при частоте процессора FCPU = 64 МГц и требуемой разрядности ШИМ N = 18 бит максимальная частота ШИМ составит:

FШИМ = FCPU / 2N = 64 МГц / 218 ≈ 244 Гц, (1)

что не обеспечит требуемые параметры. Реализация ШИМ частотой 16 кГц потребует частоту процессора порядка 4 ГГц. Максимальная разрядность ШИМ при заданных частотах процессора (64 МГц) и ШИМ (16 кГц) составит

M = Log2(FCPU/ FШИМ) = Log2(64 МГц / 16 кГц) = 11,9 (2)

что гораздо меньше требуемой разрядности.

Рассмотрим алгоритм реализации требуемого N-разрядного ШИМ (назовем его модулирующим) при генерации процессором максимально возможной разрядности ШИМ, равной M (определенной по заданным частоте FШИМ и частоте процессора FCPU, см. формулу (2)) при M < N.

N-разрядное модулирующее значение получается в результате работы алгоритма регулирования, например, по ПИД закону.

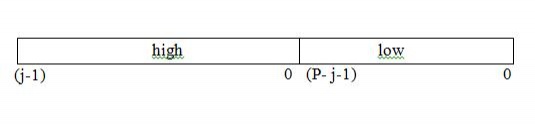

В N-разрядном числе выделим M-разрядную часть Н (старшие разряды) и P-разрядную часть L (младшие разряды) (рис.1). Модуль ШИМ настроенный на частоту FШИМ, заносится М-разрядное значение Н. Запись числа Н в модуль ШИМ приводит к генерации ШИМ с коэффициентом заполнения, пропорциональным значению Н.

Рис. 2. Разбиение N-разрядного модулирующего числа

Если изменять коэффициент заполнения M-разрядного ШИМ от периода к периоду, то результирующее значение постоянной составляющей за 2P периодов будет соответствовать ШИМ разрядности M + P = N. Таким образом, суммарный период N-разрядного модулирующего ШИМ будет равен

TΣ = TШИМ × 2P,

где TШИМ = 1 / FШИМ – период ШИМ, генерируемый процессором;

Изменение коэффициента заполнения осуществляется путем изменения числа Н, записываемого в модуль ШИМ в каждом i-м периоде:

Нi = Н + ki(L),

где ki(L) = 0 или 1 – коэффициент, зависящий от числа L, определяет добавочный бит;

i = 1 ÷ 2P.

Таким образом, необходимо сформировать 2P добавочных бит для конкретного значения L. Расчет добавочных бит ki(L) для всех возможных значений Р-разрядного числа L трудоемкая задача. Если учесть, что коэффициенты ki(L) должны быть выбраны так, чтобы 0 и 1, по возможности, были распределены равномерно по периодам ШИМ, то наиболее подходящий способ формирования коэффициента ki(L) – табличный. Так для P = 3 один из вариантов значений коэффициентов ki(L) приведен в табл. 1.

Таблица 1.

|

P

|

k1

|

k2

|

k3

|

k4

|

k5

|

k6

|

k7

|

k8

|

|

000

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

|

001

|

0

|

0

|

0

|

0

|

0

|

0

|

0

|

1

|

|

010

|

0

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

|

011

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

0

|

|

100

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

|

101

|

0

|

1

|

1

|

0

|

1

|

1

|

0

|

1

|

|

110

|

0

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

|

111

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

Требование изменения коэффициента заполнения в каждом периоде ШИМ приведет к возрастанию нагрузки на процессор: подпрограмма прерывания процессора будет вызываться с частотой FШИМ и, следовательно, к сокращению времени на реализацию основного алгоритма [6, 7].

Распределение прибавляемых бит по периодам может быть произвольным, основное правило – равномерность распределения. В этом случае наиболее рациональный алгоритм формирования прибавляемых бит – табличный. Для хранения данных таблицы коэффициентов ki(L) потребуется 2Р × 2Р = 22Р байт, если для хранения каждого бита выделить 1 байт. При упакованном хранении коэффициентов объем памяти составит 22Р × 2-3 = 2(2Р-3) байта. Упакованный вариант предполагает усложнение алгоритма выбора бита из таблицы. Даже при хранении коэффициентов в упакованном виде при Р ≥ 8 под таблицу потребуется значительный объем памяти, который является критическим параметром при разработке систем на микроконтроллерах.

При построении системы управления на микроконтроллере с малыми ресурсами, особенно на 8-разрядном, встает задача оптимизировать алгоритм формирования добавочных бит с точки зрения быстродействия и выделяемого объема памяти под таблицу.

Сократить объем памяти под хранение таблицы коэффициентов ki(L) можно, если учесть требование равномерного распределения 0 и 1 на всем периоде модулирующего ШИМ. Можно так распределить 0 и 1, чтобы появились повторяющиеся участки на этом периоде. В этом случае можно хранить в памяти только повторяющуюся часть.

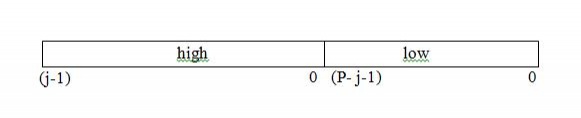

Общее число добавочных бит составляет 2Р. Разобьём Р-разрядное число, определяющее добавочные биты (рис. 2), на две части (рис.3) разрядностью j (старшая часть) и P-j (младшая часть). Тогда 2Р добавочных бит будут сгруппированы в виде 2P-j частей разрядностью по 2j, у которых одинаковое число 1, определяемых числом high, а число low определяет количество 1 присутствующих не во всех 2P-j частях.

Рис. 3. Разбиение Р-разрядной части

В этом случае объем требуемой памяти под коэффициенты (в упакованном виде) представим в виде двух таблиц:

V = 2j× 2j× 2-3 + (2P-j×2Р-j) × 2-3 = 22j - 3 + 22(P-j) - 3,

Разбиение исходного массива на два позволяет значительно сократить требуемую память под коэффициенты. Минимум памяти под коэффициенты достигается при j = P/2:

V = 22j - 3 + 22(P-j) - 3 = 2Р- 3 + 2Р - 3 = 2Р- 2

что существенно меньше первоначального размера таблицы.

Выбор длины повторяющегося участка (числа разрядов j) может быть связать с разрядностью применяемого микроконтроллера, т.к. он влияет на быстродействие системы. Поэтому, с точки зрения быстродействия, для 8-разрядных микроконтроллеров следует выбрать j = 3, определяя длину участка в один байт, для 32-разрядного j = 5, т.е. работать с 32 разрядными данными.

После того, как определились с выбором параметра j, можно сформировать таблицу повторяющихся участков из равномерно распределенных 1, количество которых (high) определено числом в этих j разрядах. Размер таблицы: 2j × 2j в битах. Например, для j = 3, размер таблицы равен 8 байт. Один из вариантов этой таблицы приведен в табл. 2, где в качестве числа high приведено содержимое j старших разряда числа L (рис. 3). В таблице у всех чисел правый бит = 0. Это выбрано с целью добавление в этот разряд бита из остаточной части low.

Таблица 2

|

high

|

Распределение добавочных бит в повторяющемся участке

|

|

000

|

0 0 0 0 0 0 0 0

|

|

001

|

1 0 0 0 0 0 0 0

|

|

010

|

1 0 0 0 1 0 0 0

|

|

011

|

1 0 0 1 0 1 0 0

|

|

100

|

1 0 1 0 1 0 1 0

|

|

101

|

1 0 1 1 0 1 1 0

|

|

110

|

1 1 1 0 1 1 1 0

|

|

111

|

1 1 1 1 1 1 1 0

|

Формирование таблицы остаточных бит из (P-j)-разрядного числа low осуществляется по тому же правилу равномерного распределения 0 и 1. В данном случае каждый добавочный бит соотносится с одной из 2P повторяющихся частей. Размер таблицы: (2P-j×2Р-j) в битах. Например, для Р = 5 и j = 3 вариант таблицы приведен в табл. 3.

Таблица 3

|

low

|

Распределение добавочных бит

|

|

00

|

0 0 0 0

|

|

01

|

0 0 0 1

|

|

10

|

0 1 0 1

|

|

11

|

0 1 1 1

|

Рассмотрим на примере формирование загружаемых модулирующих значений для N-разрядного ШИМ по предложенному алгоритму для 8-разрядного микроконтроллера [8]. Пусть N = 13, M = 8, конкретное 13-разрядное модулирующее значение равно 0110011101101, тогда:

Р = 13 – 8 = 5;

Выберем j = 3, тогда P – j = 2;

Н = 01100111;

L = 01101;

high = 011;

low = 01;

Всего следует сформировать 2Р = 25 = 32 загружаемых в ШИМ 8-разрядных значений.

Из табл. 2 по значению high выбираем повторяющуюся часть добавочных бит: 1 0 0 1 0 1 0 0. Всего повторяющихся частей: 2(P – j) = 4.

Из табл. 3 по значению low выбираем остаточную часть добавочных бит: 0 0 0 1, т.е. 1 будет добавлена только к четвертой повторяющейся части.

Сформируем добавочные биты из повторяющейся и остаточной частей:

1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 0 1 0 0 1 0 1 0 1

После окончания каждого периода 8-разрядного ШИМ из основной части Н и добавочных бит будет формироваться загружаемое значение Hi:

H1 = H +1 = 01100111 + 1 = 01101000

H2 = H +0 = 01100111 + 0 = 01100111

H3 = H +0 = 01100111 + 0 = 01100111

H4 = H +1 = 01100111 + 1 = 01101000

…

H31 = H +0 = 01100111 + 0 = 01100111

H32 = H +1 = 01100111 + 1 = 01101000

Заключение

Приведенный алгоритм позволяет при заданных ограничениях на частоту процессора и разрядность модуля ШИМ микроконтроллера реализовать на нем генерацию высокоточного ШИМ-сигнала. Приведены требования к памяти микроконтроллера, а также даны рекомендации по быстродействию системы в зависимости от разрядности процессора.

References

1. Ashanin, V. N. Sintez ∑∆-modulyatora s mnogourovnevym TsAP na osnove shirotno-impul'snoi modulyatsii signala / V. N. Ashanin, B. V. Chuvykin // Izvestiya vysshikh uchebnykh zavedenii. Povolzhskii region. Elektronika izmeritel'naya i radiotekhnika. Tekhnicheskie nauki. – 2010. – № 4 (16). – C. 97 – 105.

2. Kurashov, D. Primenenie ShIM-kontrollera IS3844 v skheme rezonansnogo preobrazovatelya / D. Kurashov // Elektronnye komponenty. – 2000. – № 5. – C. 50 – 51.

3. Di Dzhasio, L. Programmirovanie na S mikrokontrollerov PIC24: Per. s ang. / L. Di Dzhasio – K.: «MK-Press», 2012. – 320 s.

4. Prokopenko, V. S. Programmirovanie mikrokontrollerov ATMEL na yazyke S. / V. S. Prokopenko – K.: «MK-Press», SPb.: «Korona-Vek»,2006. – 208 s.

5. Trampert, V. Izmerenie, upravlenie i regulirovanie s pomoshch'yu AVR-mikrokontrollerov: Per. s nem. / V. Trampert – K.: «MK-Press», 2006. – 208 s.

6. Myasnikov, V. I. Razrabotka programmnogo obespecheniya vstroennykh sistem. / V. I. Myasnikov // Materialy Vserossiiskoi nauchno-prakticheskoi konferentsii. – Ioshkar-Ola, PGTU, 2005. – C.166-169.

7. Myasnikov, V. I. Raschet polozheniya rabochego organa manipulyatora. / V. I. Myasnikov // Materialy Vserossiiskoi nauchno-prakticheskoi konferentsii. – Ioshkar-Ola, PGTU, 2015. – s.10-14.

8. Sait podderzhki firmy Atmel [Elektronnyi resurs]. –URL: http://www.atmel.com/ ATtiny261/461/861.pdf

Link to this article

You can simply select and copy link from below text field.

|